## Simulations of a Planar Silicon Tunnel Field-Effect Transistor

<sup>1</sup>Daniel Nagy, <sup>1</sup>Antonio J. García-Loureiro, <sup>2</sup>Karol Kalna and <sup>1</sup>Natalia Seoane

<sup>1</sup>Centro Singular de Investigación en Tecnoloxías da Información, Universidade de Santiago de Compostela, 15782 Santiago de Compostela, Spain

<sup>2</sup>Nanoelectronic Devices Computational Group, College of Engineering, Swansea University, Swansea SA2 8PP, UK

daniel.nagy@usc.es

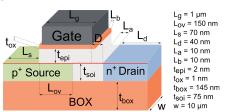

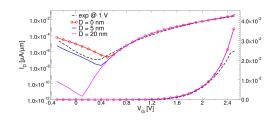

As planar metal-oxide-semiconductor field-effect transistors (MOSFETs) are scaled to the nanometre regime, their sub-threshold swing (SS) characteristics significantly degrade. This degradation causes a high power consumption limiting the performance of low power transistors in digital applications. Tunnelling-FETs (TFETs) are considered a promising solution to overcome the poor performance of MOSFETs in the sub-threshold region (leakage current (I<sub>OFF</sub>) and SS) [1] by surpassing the fundamental limit of MOSFETs of 60 mV/dec at room temperature. The on-current (Ion) of TFETs depends on the distance between the conduction and valence band because the Ion arises from a band-to-band tunnelling (BTBT) process with low efficiency. Thus the TFETs suffer from a low I<sub>on</sub> [2]-[3]. In Ref. [3], a new device structure is proposed to overcome the low IoN issue by adding an extra layer between the gate-dielectric and the p-i-n junction in order to increase the tunnelling area. The aim of this work is to investigate and optimise the performance of a TFET based on the experimental device [3]. The n-type Si TFET has a gate length of 1 μm shown in Fig. 1. The epi-layer and the SOI have an intrinsic doping of 1.0  $\times$  10<sup>15</sup> cm<sup>-3</sup>, the p-type source has a concentration of 3.7  $\times$  10<sup>19</sup> cm<sup>-3</sup> and the n-type drain of 2.7  $\times$  10<sup>20</sup> cm<sup>-3</sup>. The work function of the metal gate is 4.8 eV. All the simulations have been performed using Silvaco ATLAS [6] accounting for both the local and non-local BTBT, for the band-gap narrowing, and the thermionic emission transport model. Fig. 2 shows the  $I_D$ - $V_G$  characteristics at a drain bias of 1.0 V comparing simulations with experimental data with a very good agreement at large gate biases. The simulations allow to optimise the device architecture since I<sub>OFF</sub> increases dramatically with a drain-togate distance (D) while  $I_{ON}$  shows a minimal change.

Acknowledgment: This work is supported by the Spanish Government and FEDER funds (TEC2014-59402-JIN), by the Spanish Government (TIN2013-41129-P) and also by Xunta de Galicia and FEDER funds (GRC 2014/008).

## **References**

- [1] P. K. Singh et al., IJCET, vol. 4, no. 3, pp. 2088-2091, 2014.

- [2] J. L. Padilla et al., IEEE TED, vol. 59, no. 12, pp. 3205-3211, 2012.

- [3] Y. Morita et al., Solid-State Electronics, vol. 102, pp. 82-86, 2014.

- [4] Silvaco. (2016) ATLAS User's Manual.

## **Figures**

Figure 1: Schematic of the TFET with the corresponding dimensions. The z-direction is assumed to be a 10  $\mu$ m wide.

Figure 2:  $I_D$ - $V_G$  characteristics on both linear (right) and logarithmic (left) scales at a high drain bias of 1.0 V.